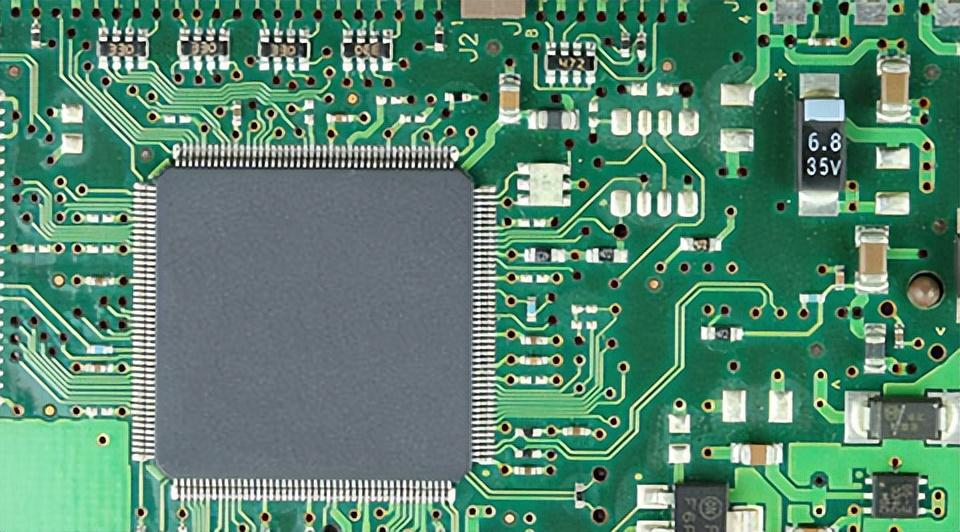

1. Lè sa a ki pa marye chip integre san pwosè itilize yon konplè ansanm nan pwosè pwosè teknoloji tankou grinding, polishing, oxidation, piblikasyon, photolithography, epitaks kwasans, Et evaporation pou simultanément pwodwi transistors, diodes, rezistans, kapisantè, ak lòt composants sou yon ti kras silicon ki pa kristal wafer, ak itilize kèk pafè izolacion pou yo isolate chak composant ak lòt nan tèm elektrik performance. Lè sa a, yon wèch aluminium te evapore sou sifas lavil la silicon wafer Et etched nan yon modèl entèseksyonen itilize photolithography teknoloji, pèmèt composants pou entèseksyone nan yon nèt sou tout pwen san bezwen, epi pwodwi yon semiconductor blan-chip integre san/sik.

An yon chip integre san

Ak devlopman de sikilasyon ki pa marye chip integre de ti jan pou mezi yo sèvi ak gwo mezi yo sèvi integre san, pwosè a teknoloji te devlope tou. Pou egzanp, piblikasyon doping remplase pa ion implantation doping pwosè; Lithographie UV konvensyonèl te devlope nan yon ansanm nèt sou tout pwen de microfabrication teknoloji, tankou microfabrication beam exposure plate fè, a ikid ki nan san etching, reyaktif ion milling, etc. Que ogmante Epitaxial tou adopte teknoloji "ultra-wo" bale moléculaire beam epitaks; itilize teknoloji depozyon chimik pou pwodwi silik polikristalin, kabòn silik ak fim sifas pasiv; Anplis pou yo itilize aluminium oswa lò, interconnection chèch lignes tou adopte pwosesis tankou Vapor chimik depozyon peuve doped polykristalin silicon chèch fim Et prèske fim fil silicid wòch, osi osi estrikti interconnection miltip.

Yon moun ki pa marye chip integre se yon sèk integre ki endepandan aplike fonksyon inite w la san bezwen pou composants externe. Pou egzekite an integrasyon ki pa marye-chip, li nesesè pou adisyon an integrasyon de rezistans, kapisantè, ak dispositive pouvwa ki fè difisil pou miniaturiser, osi byen pwoblèm isolating chak konponent de ak lòt nan tèm sikilat performance.

2. The transistor, diode, resistor, capacitor, inductor ak lòt composants de tout sikit la, osi byen menm jan interconnections yo, sont tout fè de metal, semiconductor, metal oxide, diferan metal mele fason, alloys ou insulating dielectric fim ak yon pwès de mwens pase 1 micron, Et sipèpoze pa vacuum evaporation pwosesis, sputtering pwosesis Et microplating pwosesis. Sesi integre ki fè pa pwosesis sa a te rele yon ti fim integre san. Pèmisyon pwensipal:

Sirk Entegre Film Thin

Sirk Entegre Film Thin

Ak souvan dyagram sirkel la, anvan separe l nan plizyè fonksyonal komponent dyagram, apre sa itilize a metod distribisyon planar pou konverte yo nan dezagram planar circuit pou depo yo sou substrate a. Apre sa a itilize plat fotografik la fè metod pou pwodwi pwès fim rezo modèl pou ekran imprime

D'ant 9313; pwensipal pwosesis pou pwodwisyon byen pwès fim rezon sou substrates sont prensip, sentirement, ak rezistans tuning. Souvan li te itilize pwimaj metodo se pwimaj ekran.

Pandan pwosè an ap sentire, organik la Liaison entièrement démposes Et evapores, ak la solid pèv en, démposes, Et konbine pou fòme yon dans Et fò pwès fim. Kalite ak emisyon pwès fim yo tou pwèske gen rapò a pwosè sinteri ak atmosfè anviwonman an. Fason ısınma ta dwe pa fasil pou asire konplete eliminasyon pwoblèm biologik anvan vit flux; A temps en ak tanperati pi piti selon sou dlo a ak len estrikti ki te itilize. Pou prevenite kraze fim pwès fim nan, tasyon de cooling ta dwe tou kontwole. A ki konn itilize fon en a se wouj tònel a.

D'òganize optimal rezilta nan pwès fim rezistans bezwen pou ajoute apre tire. Metòd koreksyon komen resistans enkli sandblasting, laser, Et vòltaj pulse adjustment.

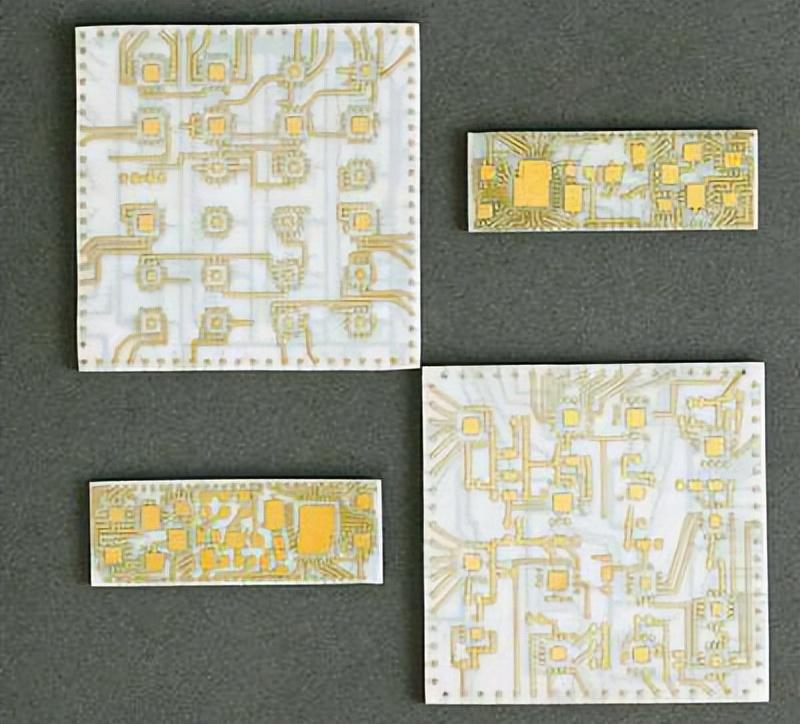

3. Fim integre san teknoloji itilize prensip ekran pou depois resistans, dielectric, ak coatings conductor sou oxide aluminium, ceramics beryllium oxide, ou carbide silicon substrates. Proces depozyon an enplike w ap itilize yon byen kado pou kreye modèl diferan fim. Modèl sa a ap fè w ap itilize metòdes fotografik, epi latex ap itilize pou bloke wòch mesh yo nan nenpòt zòn ki kote pa gen kapòt depoze. Apre netwaye, substrate alumina a pwimèt ak conductive coating pou fòm antre lignes koneksyon an, rezistans de fè soldering zòn, chip adhesion zòn, capacitor fon electrodes, ak conductor fim. Apre sa a lè'w si, pati yo te bwè nan yon tanperati ant 750 ak 950 °C pou fòm, evapore a adhesive, sinter a kondwi materyèl, epi lè sa a itilize prensip Et tire pwosesis pou pwodwi resistors, kapisantè, jumpers, insulators, ak seals koulè. Dispositè aktif yo fabrike w ap itilize pwosesis tankou faible eutectic welding, reflouvri soldering, faible stend pwen bump inversion soldering, ou kalite beam yo mennen, epi lè sa a monte sou yon substrate boule. Mountations yo Lè sa a ou soldere pou fòm pwès fim san.

pwès fim integre san

pwès fim integre san

Byen pwèske fim nan byen pwès fim san sikilasyon se jeneralman 7-40 microns. Pwoprèsis an de pweparasyon anpil wèbsayt traiter ki itilize pwès fim teknoloji se relativement konsantrasyon, ak konpatibilite de teknoloji plizyè wèbsayt] se bon, ki ka anpil amelyore dansite asanble a de entegrasyon segondè. Anplis, prèske a ikid ki nan san, résumé regle, imprimasyon ak pat pwosesis yo tout nouvo pwèske fim pwosesis teknoloji. Ak menm jan anpil fim integre san, byen pwès fim integre san tou itilize pwosesis hybrid paske pwès fim transistor yo pa ankò praktik.

4. Preferans pwosesis: Chip santi integre circuit Et chèch fim ak pwès fim integre circuit chak gen pwòp karakteristik yo epi ka complement youn ak lòt. Quantité de circuits jeneral Et estanda sikil se gwo, ak moun ki pa marye chip integre san ka itilize. Pou faible pèchase ou ki pa estanda san circuits, yon hybrid pwosesis jeneralman itilize, ki enplike w ap itilize estanda-chip entegre circuits Et hybrid entegre circuits ak aktyèl Et pasive composants. Fim fason ak ti fim integre avec ansanm ak lòt nan kèk aplikasyon. Enpòtman pwosè ki te itilize nan byen pwès fim teknoloji se relativement senp, devlope an se fleksib, bisiklèt pwodwi a se kout, Et chalè a dissipation se bon. Se poutèt sa, li widely itilize nan circuits ak wo vòltaj, anwo pouvwa anwo, Et mwens aksyon tolans pou composants pasive. An adisyon, akoz de fason pou achiv mwens plizyè wèbsèt wiring nan pwosè pwodwisyon de pwès fim san/sik, gwo-échelle integre mwayèn chips ka être asanble nan ultra gwo échelle integre san nan plis konplèks aplikasyon an tou dèyè kapabilite de moun ki pa marye-chip integre san/sik. youn ou pli fonksyonèl youn chip integre san/chip kapab tou être asanble nan plizyè fonksyonèl composants ou menm ti machin.

5. itilizyon ak pwoteksyon: (1) EnIntegrated circuits yo pa pèmèt yo exceed limit yo pandan itilizyon. Lè enfòmasyon vòltaj enfòmasyon vòltaj chanje pa pa plis pase 10% nan valè te evalye, paramèt elektrik yo ta dwe complète ak valè espesyalize yo. Lè anviwonman pouvwa ki te itilize nan san an active Et nèt, pa dwe gen pa vòltaj istantani te pwodwi, annik konsa li ap koze sèk la pou kraze.

(2) Operasyon tanperati de entegre circuit se jeneralman ant-30 ~85 °C, e yo ta dwe enstale tou lwen de chalè sous ke kapab.

(3) Lè m' ap rezoud entegre san, déclenche irons ak yon pouvwa pi gran pase 45W pa ta dwe itilize, Et la kontinye déclenche tan pa ta dwe sipète 10 segond.

(4) Pou MOS integre san, li nesesè pou prevence baryè electrostatic induction kraze.

Owo a se yon enfòmasyon pou enfòmasyon sékir teknoloji integre. Nan kounye a, moun ki pa marye chip integre san se pa sèlman devlope pou pi gwo enfòmasyon, men tou kont anwo pouvwa a, liyèn, fréquence anwo nan syèl la ak analog san. Sepandan, tèm microwave entegre circuit Et anwo pouvwa integre san, chèch fim ak pwès fim hybrid entegre circuit toujou gen avantaj. Nan chwazi espesifik, diferan kalite jan de sèk ki pa marye chip integre sont souvan konbine ak pwès fim ak ti fim integrasyon pwosesis, espesyalman presyon rezistans ret ak rezistans rezistans ak substrates rezistans rezistans tete ak substrates konbine nan byen pwès rezistans fim ak bann conduction pou fòme yon konplèks epi konplèks sikit. Lè nesesè, ultra composants grenn pa grenn ka menm être konekte pou fòm pati ou tout machin la.

English

English Spanish

Spanish Arabic

Arabic French

French Portuguese

Portuguese Belarusian

Belarusian Japanese

Japanese Russian

Russian Malay

Malay Icelandic

Icelandic Bulgarian

Bulgarian Azerbaijani

Azerbaijani Estonian

Estonian Irish

Irish Polish

Polish Persian

Persian Boolean

Boolean Danish

Danish German

German Filipino

Filipino Finnish

Finnish Korean

Korean Dutch

Dutch Galician

Galician Catalan

Catalan Czech

Czech Croatian

Croatian Latin

Latin Latvian

Latvian Romanian

Romanian Maltese

Maltese Macedonian

Macedonian Norwegian

Norwegian Swedish

Swedish Serbian

Serbian Slovak

Slovak Slovenian

Slovenian Swahili

Swahili Thai

Thai Turkish

Turkish Welsh

Welsh Urdu

Urdu Ukrainian

Ukrainian Greek

Greek Hungarian

Hungarian Italian

Italian Yiddish

Yiddish Indonesian

Indonesian Vietnamese

Vietnamese Spanish Basque

Spanish Basque